|

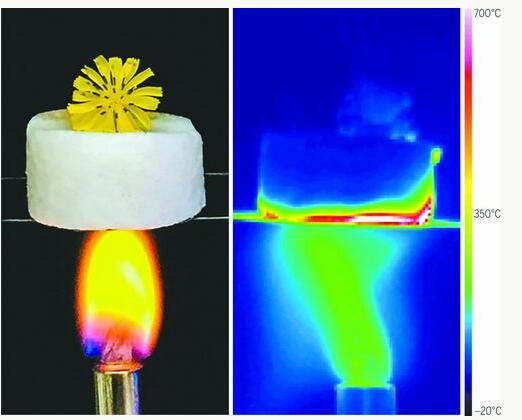

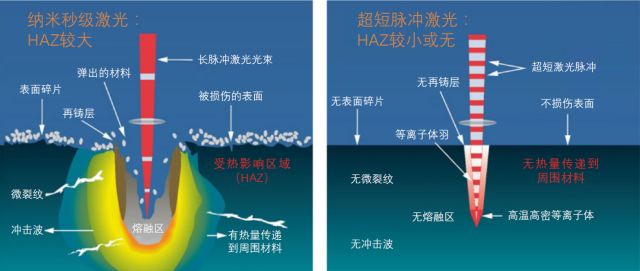

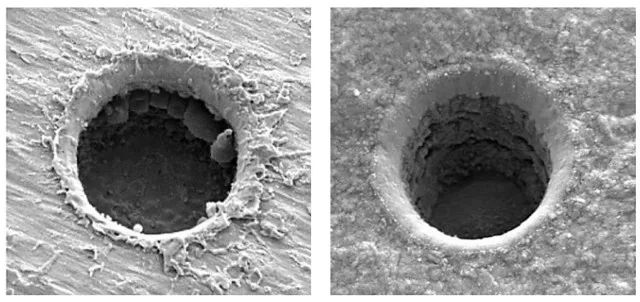

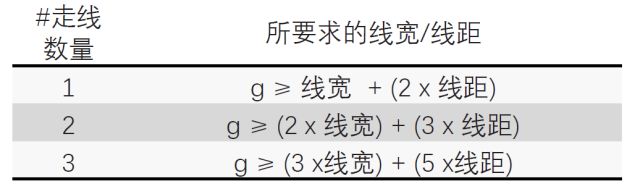

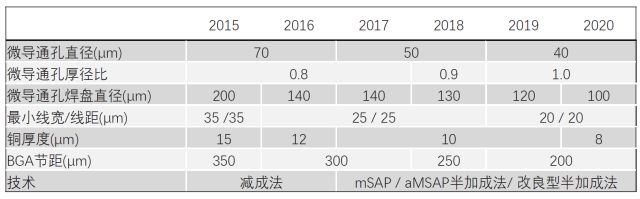

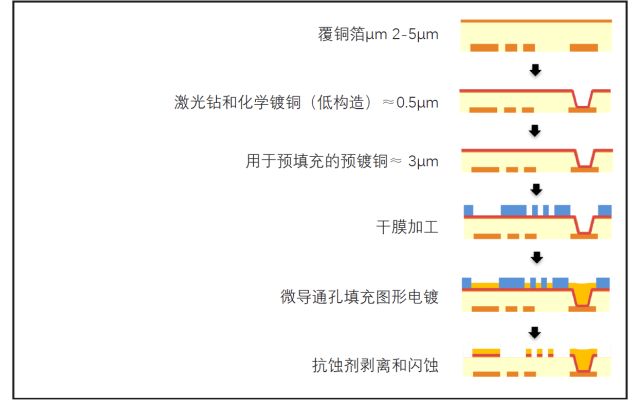

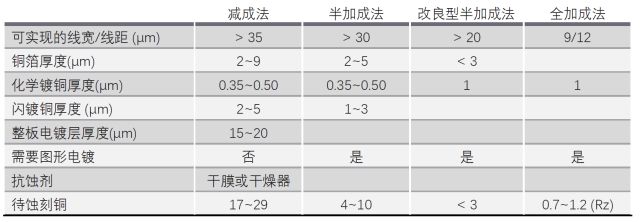

PCB生产有许多其他发展趋势,所有这些都关乎制造的关键工艺,并将影响HDI设计的发展。 使用已建立的成套工具,今天大多数的微通孔都是由二氧化碳激光器形成的。 该工艺的一个缺点是会在载板内产生大量的热量,这将导致在每个钻孔位置形成热影响区(HAZ),因此会影响最小导通孔节距、尺寸,以及质量。  图1:激光脉冲持续时间对HAZ的影响 (来源:IPG Photonics) 为了解决这个问题,激光器制造商正在开发具有超短脉冲(USP)激光器的新工具,该工具用皮秒或飞秒脉冲代替现有的纳秒脉冲。 这种激光系统可以形成更小的导通孔,同时更小的HAZ产生,这意味着可以大大减小微通孔节距,并且随着激光吸收的改善,导通孔获得更好的质量,具有更少的表面碎片或“飞溅”。 随着这些激光系统的出现,微通孔密度的性能将提升至另一高度,从而实现HDI性能的大幅提升。  图2:用纳秒激光(l)和USP激光(r)形成的典型微通孔(来源:Orbotech) 形成微通孔后,下一个问题就是电镀。虽然导通孔没有显著的厚径比变化,通常保持在0.7~0.8,但它们的尺寸不断减小,这对电镀来说是一种挑战。一个重要的发展是能够用铜完全填充导通孔,这使得导通孔能够直接相互堆叠。这一点影响很大,堆叠导通孔是HDI设计的组成部分,因为它们可以节省空间,特别是与交错导通孔相比,改进了热和电气管理,其上佳的表面平整度也有助于最终的组装良率。 最近的一项电镀新进展是通孔填充(THF)工艺的发布。实芯铜柱将改善热关键区域的导热性,从而改善冷却效果,并且因为仍然可能使用焊盘内导通孔,THF还可支持增加的I/O密度。  图3:堆叠的导通孔和通孔填充 BGA设计规则 在许多情况下,项目的关键设计参数通常与该设计中的其他方面相关联, HDI PCB也不例外。在这种情况下,其控制因素是BGA的焊盘尺寸和节距。 通过表1我们可以看出焊盘尺寸与可能的走线宽度之间的关系,具体取决于焊盘之间通过的走线数量。对于“简单”或低I/O数的封装(图6a),我们只需要在BGA焊盘之间布一条走线,很明显最大走线宽度是焊盘之间可用空间的1/3。在给出的实例中,焊盘节距300mm,焊盘直径为150mm,因此建议的线宽和线距要求为50mm。  表1:指定焊盘尺寸所要求的线宽/线距  图4:走线对尺寸的影响(来源:Altera) 如果我们现在使用一个更复杂的封装,其更多的I/O数要求在同样的焊盘节距内布两条走线,那么推荐的线宽/线距就会下降至30µm,并且很明显,随着焊盘节距的减小,将进一步限制线宽和线距。 总的来说,新激光工具的可用性将允许更小的微通孔更密地排列在一起。这将有助于采用更小的BGA焊盘,与更多的 I/O数器件相结合,减小线宽/线距的需求,这将推动HDI路线图(图7)的发展,并继续从现有的每层生产布线转变为半加成法工艺。  图5:HDI路线图中的关键因素(资料来源:IPC、JISSO、AtoTeCo、客户群) ELIC、任意层和半加成法 目前大多数HDI PCB使用减成法ELIC(每层互连)或任意层技术进行生产。 一般流程如图8所示。  图6:ELIC工艺流程的通用示意图 高端HDI PCB需要线宽/线距从40 mm下降到30 mm,而目前的电镀工艺无法实现这一目标,因此需要转换到半加成法工艺。由于这些工艺在IC载板生产中很常见,因此HDI板被称为类载板的PCB(SLP)。 图9显示了基于半加成法(mSAP)工艺的SLP生产通用工艺。  图7:基于mSAP的类载板工艺的概要示意图 工艺挑战 很显然,半加成法(mSAP)工艺与传统的PCB生产路线有相同的步骤,因此原则上,更新和扩展现有设施使从减成法生产到半加成法(mSAP)生产的转变显得相当简单。然而,由于涉及许多变化,这种观点通常是错误的,从最近正进入类载板供应链的公司已经证明了这一点。必须为半加成法(mSAP)工艺量身定制的新设备和流程,同时在进行投资时充分考虑半加成法(mSAP)工艺的预期生命周期问题。幸运的是,这些可以修改为改良型半加成法(amSAP),该方法可以实现>20 mm 的线宽/线距,并且只需要有限的进一步投资。  表2: PCB生产工艺要点对比 表2显示了可用技术的简单对比,包括其性能和主要差异。 对于那些希望进入类载板供应链并开始提供电路板的公司,存在许多需要克服的挑战,其中有些可通过投资得以解决,而其他挑战只能通过与经验丰富的供应商合作来解决。 改进的激光钻孔 虽然新一代激光钻孔机还未出现,目前的二氧化碳设备仍是微通孔加工的主力。 为了满足半加成法(mSAP)中铜箔厚度的降低,可以用化学工艺预处理铜表面,以最大化二氧化碳激光吸收并改善孔形状,同时确保后续电镀操作的最佳条件。 优化的PTH 微通孔中可靠的PTH覆盖不仅对半加成法(mSAP)生产至关重要,而且导通孔尺寸的预期减小以及介电材料范围的扩大意味着化学镀铜工艺也需要审查。结合优化预处理系统的稳定活化系统将需要与高分散力化学镀铜槽一起合作,以确保无论是在垂直方向或更常见的水平方向的导通孔覆盖。 图形电镀铜 填充导通孔,即全通孔或堆叠微通孔对于手机用PCB设计是必不可少的。然而,对于类载板,导通孔填充必须与细走线图形电镀和极佳的表面均匀性一起实现,所有这些都需在可接受的电镀时间内完成。 细走线形成 小于30μm的走线须采用精细线路成像工艺,这对于减成法工艺来说并不常见。低蚀刻表面处理辅助干膜附着,需要新型抗蚀剂和剥离剂以确保没有干膜残留物,而受控的蚀刻工艺必须能够形成最终的图形而不会有过蚀或线宽损失。 改进层粘接 在更精细的图形、更高的布线密度和更高的运行频率的推动下,SLP工艺必须尽可能最小化铜残,尽可能通过低表面粗糙度来最大化信号完整性。 高分辨率表面涂层 由于SLP具有更精细的特征,最后的表面涂层也必须确保兼容性,在大多数情况下这意味着没有额外的镀层(镍脚)。这与增强的抗腐蚀性和可控的金厚度相结合,使得新一代的ENIG化学品成为高端PCB应用的首选。 |

收藏

收藏 打印

打印