|

摘要 在激光雷达应用领域,高功率密度垂直腔面发射激光器(VCSEL)越来越受到关注。多结VCSEL是获得高功率密度的关键技术。为了得到高性能多结VCSEL阵列,高斜率效率、高填充因子和小发散角是主要的研究方向。我们优化了外延设计和流片工艺,如隧道结、氧化层和阵列布局。本文报道了激射波长在940nm附近的高性能多结VCSEL阵列。作为激光雷达应用的基本光源,选择性氧化的正面发射VCSEL阵列已实现,其具有59.7%的光电转换效率和8.3W/A的斜率效率。加工后的VCSEL阵列器件的发光面积为234* 250um2,15A峰值电流,10KHz 10ns(半峰宽)的脉宽测试条件下,功率密度大于1800W/mm2。发散角小于21度(1/e2)。

关键词: 激光雷达,垂直腔面发射激光器阵列,多结,高功率密度,小发散角

01 背景介绍

近年来,随着激光雷达(LiDAR)技术的发展,VCSEL阵列光源,由于其低制造成本、小温漂系数、易于二维集成的优势,越来越受到激光雷达应用市场的关注。首先,使用特殊的结构和工艺设计,VCSEL阵列可以实现更高的功率密度和更低的发散角,以满足激光雷达长距离应用的发展需求,利用多结VCSEL技术是产品实现更高效率、更高功率密度的关键。其次,使用特殊的结构设计,如优化氧化层的位置、厚度、Al组分,发散角性能可以进一步优化。最后,更高的填充因子意味着更小的芯粒面积,也有利于更高的输出功率密度。考虑到纳秒级的短脉冲测试条件,VCSEL阵列的热积累可以忽略。大的氧化孔径和小的周期尺寸也可以用于提高填充因子。

本文中,通过优化外延结构设计和制造工艺的VCSEL阵列可以实现高功率密度和低发散角。在晶圆级100Hz 10us的宽脉冲测试条件下,VCSEL阵列的能量转换效率峰值高达59.7%,斜率效率高达8.3W/A。另外,在器件级10KHz 10ns短脉冲测试条件下,VCSEL阵列可以实现高于110W的峰值功率输出,对应的功率密度高于1800W/mm2,发散角达到21°。

02 高光束质量的多结VCSEL阵列设计 2.1 应用需求

激光雷达是一种利用激光成像技术进行精准距离量测的技术,被认为是智能驾驶、3D传感等领域最重要的探测技术之一。随着探测距离的增加,点云(Point Cloud)密度随之降低,分辨率也会受到限制。为了实现远距离3D扫屏的重建,就需要具有更高功率密度、更低发散角的高质量激光光束。

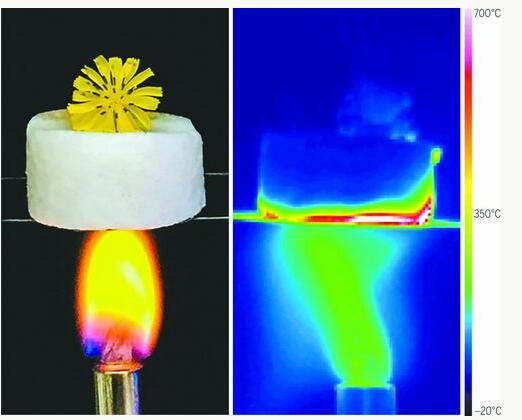

设计理念如图1所示。使用纳秒级短脉冲测试,具有小发散角的多结VCSEL阵列为激光雷达的应用提供了一个极佳的平台。基于此理念,我们设计并制造了世界领先的多结VCSEL阵列(5/6/8结),并利用特殊的氧化层和填充因子设计来实现更高功率密度和更低的发散角性能。

图 1. 激光雷达光源探测示意图,左为常规,右为更高功率密度、更小发散角优化结果。

2.2 器件光电性能

2.2.1 效率优化

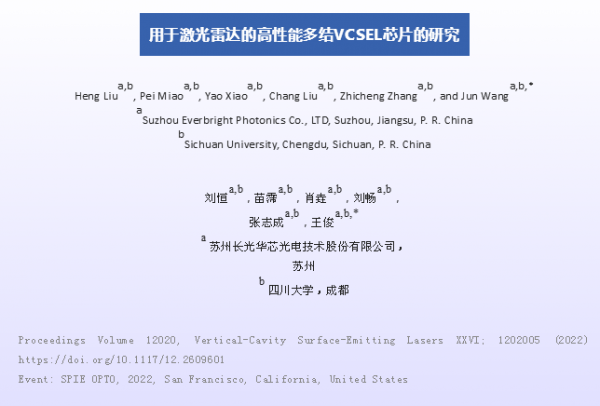

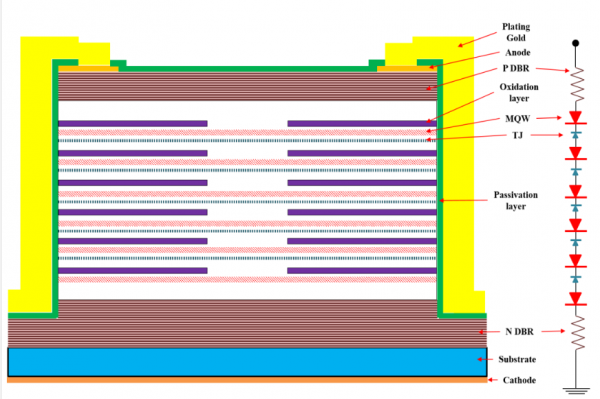

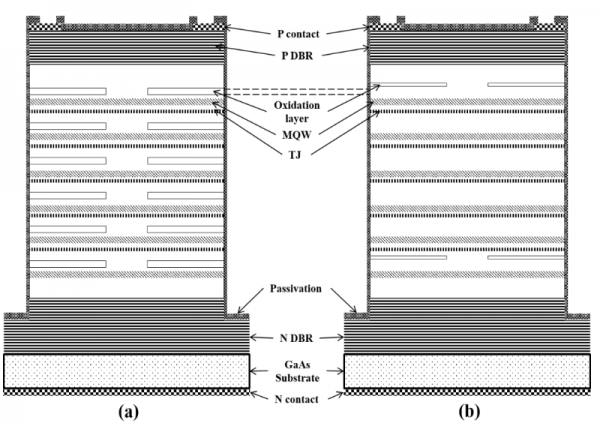

为了提高能量转换效率(PCE)和斜率效率(SE),通过多个有源区的堆叠,可以增大器件的增益体积。我们的多结结构设计中,利用了低串阻、低吸收的隧道结设计,并利用了外延层厚度精准控制技术实现增益介质与增益光场的对准。6结VCSEL阵列的结构示意图和等效电路图如图2所示。

图 2.6结VCSEL结构示意图和等效电路模型。

2.2.2 发散角优化

对于传统的多结VCSEL阵列,发散角会随着隧道结和量子阱数量的增多而变大。基于文献报道和我们的仿真实验结果,VCSEL阵列的发散角会受到氧化层指标的影响,如位置、厚度、Al组分和数量等因素,如图3所示。图3a给出了传统6结VCSEL的结构示意图,上述氧化层指标影响到“纤芯”(中心区域)和“包层”(氧化区域)的有效折射率差值。另外,引入了不同位置的增益损耗比,基横模和高阶横模的分布位置也会发生变化。尽量扩大基横模的占比,有利于发散角的优化。

图 3.发散角优化机理。(a)传统6结VCSEL的结构图,(b)针对发散角性能的优化结构。

2.2.3 填充分子优化

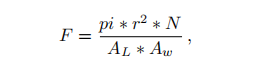

填充因子定义为总发光窗口面积除以总发光面积。总发光窗口面积取决于每个发光孔的氧化孔径,总发光面积取决于光束阵列的外径。

公式1

其中F是填充因子,r是氧化孔径的半径,N是发光点数量,AL是总发光面积的长,Aw是总发光面积的宽。

公式2

其中J是电流密度,Io是工作电流。

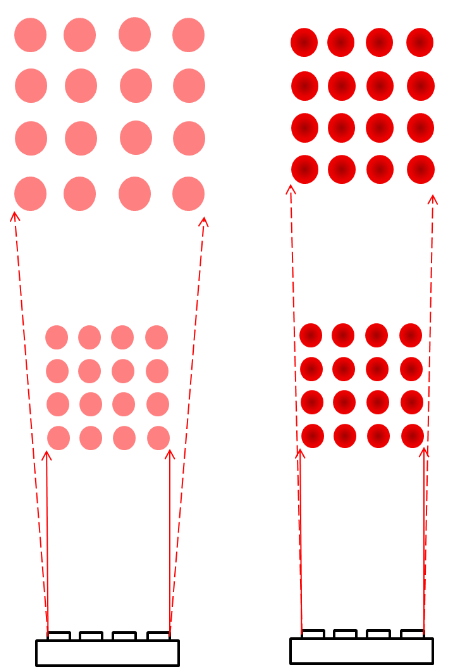

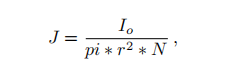

从公式1和2可知,对于给定的总发光面积,低的填充因子会导致较高的电流密度,会导致器件工作在高电流密度模式。在此工作模式下,损坏的可能性会增大,影响器件可靠性。第二,高的电流密度,更容易出现增益饱和现象,尽管低于激光雷达的实际工作电流,但是转换效率和斜率效率也会受到影响。第三,高的填充因子,会降低器件串阻,可以为驱动电路板的电压限制提供更大的空间。我们调整氧化孔径的尺寸,台面尺寸和发光阵列的周期,以实现高填充因子的VCSEL阵列版图,如图4c所示。图4中,从a,b到c,填充因子依次分别为27.0%,42.0%和48.8%。

图 4.填充因子优化机理。a)填充因子为27.0%的版图设计,b)填充因子为42.0%的版图设计,c)填充因子为48.8%的版图设计。

2.3 工艺流片

流片工艺如图5所示。 a. GaAs基底上的外延生长。 b. 背面Ti和SiN的应力补偿。P型接触金属被沉积在p+金属层的表面。 c. 干法刻蚀产生台面。 d. 氧化炉管进行氧化工艺。 e. PECVD生长SiN钝化层。 f. ICP-RIE刻蚀形成电流注入通孔。 g. 种子金沉积和金电镀用于电流注入。 h. 研磨抛光衬底后,N型接触金属被沉积在N侧。

图 5.工艺流程图。

03 不同设计的结果讨论 3.1 高效率

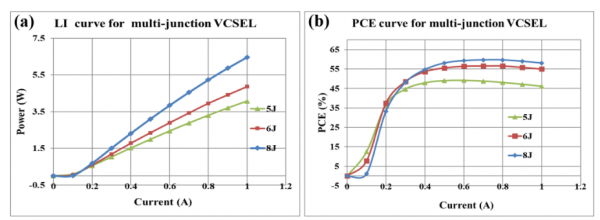

我们针对5/6/8结的VCSEL阵列完成流片工艺。图6给出了100Hz 10us脉冲电流驱动下的5/6/8结VCSEL阵列的对比。随着更多结数的设计,斜率效率从4.9W/A,提升到5.9W/A,最终提升到8.3W/A,如图6a所示。最大转换效率从48.7%,提升到56.5%,最终提升到59.7%,如图6b所示。

图6.100Hz 10us脉冲电流驱动下的5/6/8结VCSEL阵列LI和PCE曲线。a)LI曲线,b)PCE曲线。

3.2 低发散角

为了证明基于不同氧化层位置的发散角优化设计,我们增大了波导层厚度,保证氧化层和有源区的光学距离为0.25lambda,0.75lambda,和1.25lambda。如图7所示,使用10kHz 10ns短脉冲测试条件,发散角分别优化至27.9°、26.6°和24.6°。

图7.短脉冲驱动下不同氧化层位置对发散角的影响。

3.3 高填充因子

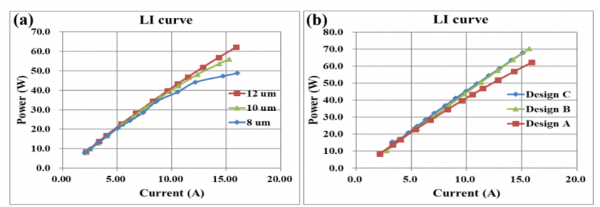

针对图4中的a/b/c三种结构,我们进行了5结的VCSEL阵列流片。并根据不同的台面尺寸实现不同的氧化孔径。考虑到给定的VCSEL阵列布局,图8a中给出了8um/10um/12um氧化孔径下的LI曲线。在10kHz 10ns短脉冲测试条件下,使用小的氧化孔径,如8um,由于相对较大的电流密度,斜率效率降低。另外,针对不同填充因子设计的A,B,C结构,其LI曲线如图8b所示。在一定范围内,斜率效率会随着填充因子的提高而提高。

图8.不同填充因子设计的LI性能对比。a)不同氧化孔径尺寸下的LI曲线,b)不同填充因子版图设计A、B、C的LI曲线。

04 高性能8结VCSEL阵列和高量产能力

4.1 优化后8结VCSEL阵列的性能

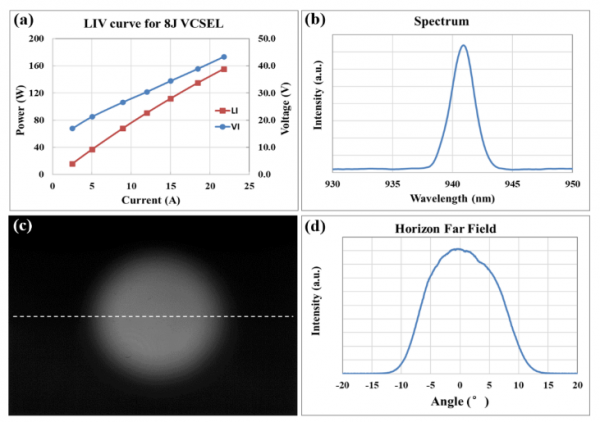

综合上述优化机理,我们实现了具有高功率密度、高斜率效率、低发散角的8结VCSEL阵列。其性能测试条件为10kHz 10ns短脉冲测试。如图9a所示,15A的驱动电流下,输出总功率为112W,功率密度超过1800W/mm2,转换效率为21%。同时,其远场分布图如图9c所示,发散角性能如图9d所示,小于21°。

图9.8结VCSEL阵列的短脉冲测试性能。a)LIV曲线,b)光谱曲线,c)远场光斑的CCD图像,d)远场光斑强度分布。

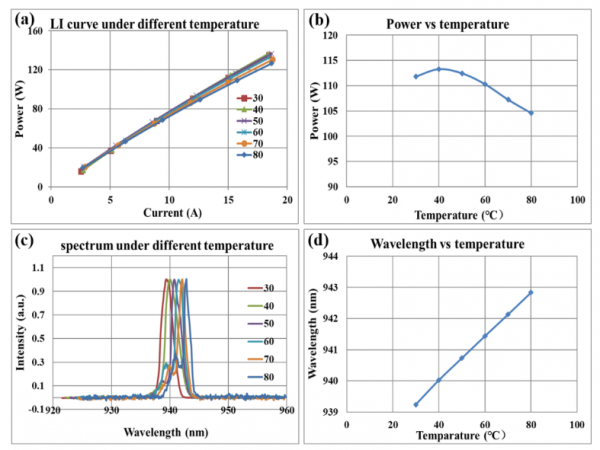

考虑到纳秒测试条件,器件的热累积可以忽略。为了研究不同温度下的阵列性能,我们使用了TEC提供从30C到80C的环境温度。10kHz 10ns短脉冲测试中,LI、FF和光谱性能如图10所示。图10a展现了8结VCSEL阵列极高的稳定性。在工作条件15A下,其功率波动范围小于8%,如图10b所示。波长随温度漂移的曲线如图10c所示,系数为0.07nm/C,如图10d所示。

图10. 8结VCSEL阵列的变温性能。a)不同温度下的LI曲线,b)功率随温度变化曲线,c)光谱随温度变化曲线,d)波长漂移与温度关系。

4.2 VCSEL芯片的高量产能力

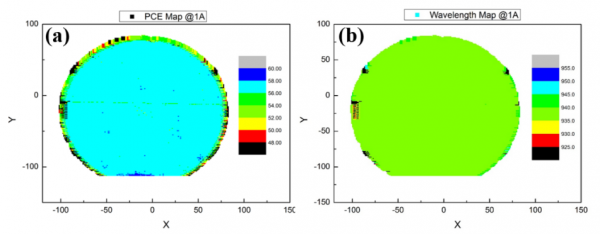

目标激光雷达产品,图11给出了6吋晶圆上能量转换效率和波长分布的均匀性,显示了苏州长光华芯光电技术股份有限公司6吋生产线极好的量产控制能力。图11a表明,超过95%的器件工作状态下的能量转换效率介于54%和58%之间。图11b表明,超过95%的器件工作状态下的波长分布介于935nm和945nm之间。

图11.6吋晶圆VCSEL阵列的均匀性。a)PCE Map,b)波长Map。 05 总结

本文设计并制造了用于激光雷达应用的高能量密度和低发散角的多结VCSEL阵列,优化后的最大能量转换效率为59.7%,斜率效率8.3W/A。测试条件为100Hz 10us宽脉宽驱动。对于8结VCSEL阵列产品,10kHz 10ns短脉冲驱动15A的工作电流下,其功率密度高达1800W/mm2,发散角小于21°(1/e2)。针对波长、能量密度、发散角和其他主要性能参数,可以随客户需求进行定制服务。

致谢 作者感谢苏州长光华芯光电技术股份有限公司VCSEL团队在器件设计、流片工艺、封装及测试方面的工作。

参考文献 |

收藏

收藏 打印

打印